AMS Verification

Analog-Mixed Signal (AMS) verification is one of the most demanding and risk-sensitive phases of semiconductor development. Unlike digital verification, AMS requires validating analog behavior, noise tolerance, precision, dynamic conditions, linearity, PVT robustness, and system-level interaction simultaneously. Any mismatch between the design intent and silicon behavior can cause functional failures, noise issues, yield loss, higher leakage, or expensive mask re-spins. That’s why AMS verification today is not just a step—it is a mission-critical requirement for achieving reliable first-silicon results.

At Siliciom, we specialize in end-to-end AMS verification that ensures your analog and mixed-signal IP blocks meet precision, power, performance, reliability and manufacturability targets before tape-out.

Core Capabilities

Block-Level AMS Verification

- Op-amps, comparators, bandgap

- High-speed PLL/ADC/DAC

- Power and RF analog blocks

Mixed-Signal SoC Verification

- Analog-digital co-simulation

- Interface and clock network validation

- Full-chip mixed-signal environments

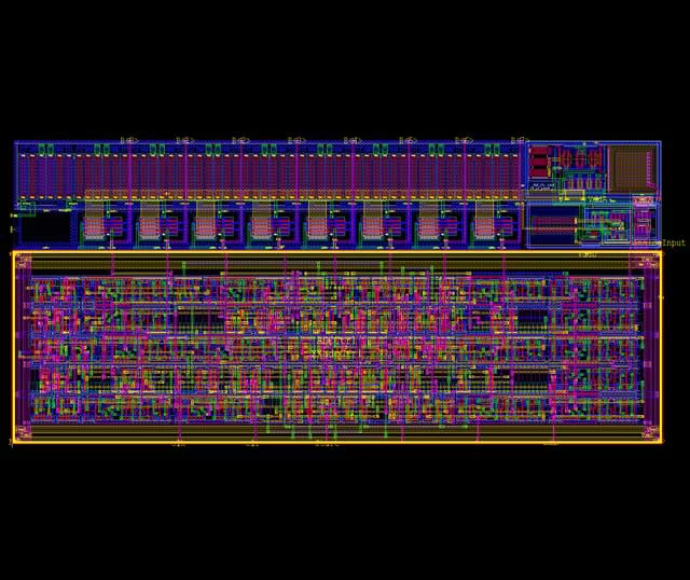

Parasitic & Layout-Aware Verification

- RC extraction, LDE effects

- Crosstalk, noise and jitter validation

- Power-performance trade-off analysis

PVT & Statistical Verification

- Full PVT corner simulations

- Monte-Carlo-based yield estimation

- Variation-aware performance analysis

AMS Modeling & Abstraction

- Verilog-A/MS behavioral models

- Faster simulation environments

- Accurate mixed-signal abstraction

Sign-off Verification

- DRC/LVS physical correctness

- Pre-tapeout validation

- Power and RF analog blocks